Cadence Digital Design Implementation (DDI) System 23.14.000-ISR4 – Advanced SoC Physical Design Suite for Linux

Cadence Digital Design Implementation (DDI) System is an all-in-one installation of three industry-leading tools—Genus Synthesis Solution, Joules RTL Power Solution, and Innovus Implementation System—providing engineers with seamless integration and a unified environment to address the growing complexity of digital SoC (System-on-Chip) design.

This suite is built to deliver high-quality chip designs that meet aggressive Power, Performance, and Area (PPA) targets, while accelerating time-to-market.

🧩 What Is Cadence DDI System?

The DDI System combines:

- Innovus for physical implementation

- Genus for RTL synthesis and early physical-aware synthesis

- Joules for RTL-level power estimation and analysis

Together, these tools provide a tight integration for advanced design tasks like:

- Physical-aware synthesis and optimization

- Cross-stage timing correlation

- Datapath area reduction

- Power-aware design exploration

🧰 Key Features of Cadence DDI System

🔧 1. Innovus Implementation System

- Massive parallel physical implementation engine

- Delivers high-quality, high-performance layout results

- Targets aggressive PPA metrics

- Fully supports iSpatial, physical re-synthesis, Power Replay, and Smart XOR technologies

- Accelerates convergence from RTL to GDSII

🔧 2. Genus Synthesis Solution

- Next-gen RTL and physically-aware synthesis tool

- Up to 10x RTL design productivity and 5x faster runtime

- Precise timing and wirelength correlation (within 5% of final layout)

- Reduces iteration loops between block-level and top-level synthesis by up to 2x

- Achieves up to 20% datapath area savings with no performance compromise

🔧 3. Joules RTL Power Estimation

- Accurately estimates RTL power early in the design cycle

- Provides system-level analysis of power trends across design stages

- Enables correlation from RTL to final implementation

- Integrates with Cadence Palladium and Stratus HLS platforms for early power modeling

🧠 Benefits for Design Teams

- Unified toolchain for consistent design goals across synthesis, power estimation, and layout

- Reduces design cycle time and improves RTL-to-signoff predictability

- Ideal for SoC and ASIC design, where high performance and low power are critical

- Trusted by leading semiconductor and system design companies

💻 System Requirements

- Platform: Linux (RHEL/CentOS preferred for enterprise environments)

- Architecture: x86_64 (64-bit)

- Recommended Configuration:

- Multi-core CPU (Intel Xeon or AMD EPYC)

- 64 GB RAM or more (128 GB+ for large designs)

- SSD or high-speed storage

- Dedicated GPU optional (for GUI acceleration)

⚠️ Note: Ensure system compatibility with Cadence installation prerequisites (license server, environment variables, and required dependencies like glibc, X11, and C-shell).

See Also:

CFTurbo v2025 R1.2.114 + CFTurbo FEA v2024 R1.0 x64

Nik Collection by DxO 8.0.12 (Win) / 6.1.0 (macOS)

📦 What’s Included

- Cadence DDI System v23.14.000-ISR4 Installer

- Full suite: Innovus + Genus + Joules

- Advanced technology node libraries and examples

- Documentation and training modules

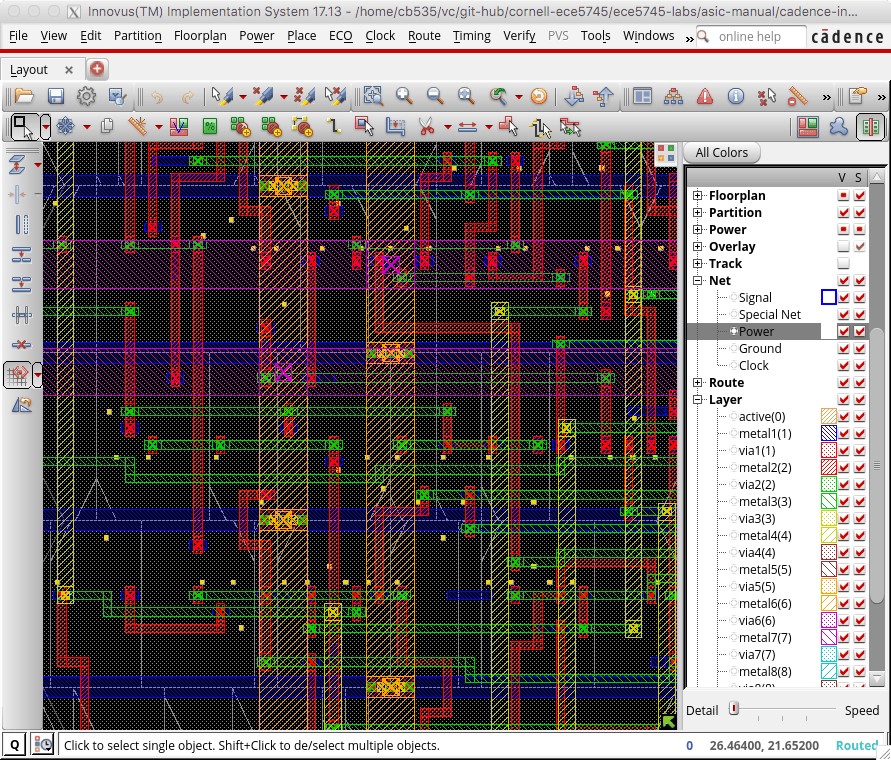

Cadence Digital Design Pictures:

👤 Who Should Use Cadence DDI?

- ASIC/SoC designers working on large-scale designs

- Physical design engineers focused on achieving optimal PPA

- RTL designers requiring early power feedback

- EDA professionals involved in backend flow development

- High-performance chip development teams working in AI, 5G, automotive, or HPC

Cadence DDI System 23.14 offers a powerful, unified, and scalable environment for tackling the demands of next-generation silicon. With deep tool integration and parallel performance optimization, it enables teams to innovate with confidence and speed.

Installation Guide

Read the Readme file in the Crack folder.

Cadence Digital Design Download link

Official: Cadence Digital Design Implementation

Alternative: Cadence Digital Design Implementation

File size

23.2 GB